Advce on push-pull gate driver

Posted by bobc

|

Advce on push-pull gate driver January 21, 2014 06:34PM |

Registered: 12 years ago Posts: 1,236 |

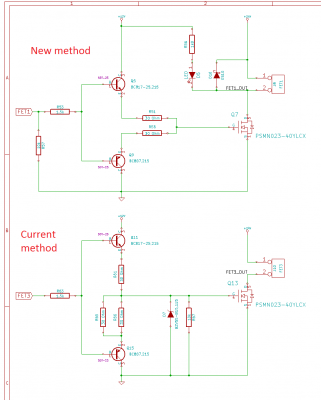

I'm doing a little work on the Decapede project. I don't understand some features of their MOSFET gate driver although it looks like it should be a standard totem pole driver, so I am seeking advice. Here is the current driver and my proposed new driver (in reverse order!)

I don't know if I am missing something obvious, but the things that puzzle me are:

1. The 15V zener diode D7 seems to be superfluous, I can't see it ever does anything. The gate voltage should never go above 12V.

2. The pull down R67 also seems ineffective, since 12V is derived from 24V. OTOH, FET3 might not be driven by the CPU or have pull ups enabled, so I moved the pull down to the input, which is what we do now on RAMPS_FD.

3. The 3 resistors R61, R65 and R66 are 1210 packages. I can't see why they need to be, 0805 should work fine here?

4. I can't see a need for R65 and R66, or why there is 15R on the low side and 30R on the high side.

5. I added a flyback diode D16 across the output, they definitely help reduce voltage peaks

So I think my new method should perform better and have a smaller footprint. Any comments?

What is Open Source?

What is Open Source Hardware?

Open Source in a nutshell: the Four Freedoms

CC BY-NC is not an Open Source license

I don't know if I am missing something obvious, but the things that puzzle me are:

1. The 15V zener diode D7 seems to be superfluous, I can't see it ever does anything. The gate voltage should never go above 12V.

2. The pull down R67 also seems ineffective, since 12V is derived from 24V. OTOH, FET3 might not be driven by the CPU or have pull ups enabled, so I moved the pull down to the input, which is what we do now on RAMPS_FD.

3. The 3 resistors R61, R65 and R66 are 1210 packages. I can't see why they need to be, 0805 should work fine here?

4. I can't see a need for R65 and R66, or why there is 15R on the low side and 30R on the high side.

5. I added a flyback diode D16 across the output, they definitely help reduce voltage peaks

So I think my new method should perform better and have a smaller footprint. Any comments?

What is Open Source?

What is Open Source Hardware?

Open Source in a nutshell: the Four Freedoms

CC BY-NC is not an Open Source license

|

Re: Advce on push-pull gate driver January 22, 2014 02:16AM |

Registered: 14 years ago Posts: 1,092 |

IMO the zener is there to limit the gate voltage to 15V.

The only way I could see that happening is getting drain to gate leakage on the FET that is being driven. No idea how likely that is in this setup.

Might be worth looking at one of those integrated driver chips that were discussed in the RAMPS-FD thread. Probably cheaper, definitely less component count, and simpler to integrate.

Edited 1 time(s). Last edit at 01/22/2014 02:16AM by Cefiar.

The only way I could see that happening is getting drain to gate leakage on the FET that is being driven. No idea how likely that is in this setup.

Might be worth looking at one of those integrated driver chips that were discussed in the RAMPS-FD thread. Probably cheaper, definitely less component count, and simpler to integrate.

Edited 1 time(s). Last edit at 01/22/2014 02:16AM by Cefiar.

|

Re: Advce on push-pull gate driver January 28, 2014 03:33AM |

Registered: 13 years ago Posts: 1,352 |

About the zenner one, i think could use the circuit with supplies more than 15v, while keeping the gate at just 15v, as long as the current through the upper 30ohms resistor gives less power than rating of the zenner.

But, there should be no need to have the fall time with 2 paralel resistors, i dont see why. Normally the fall time is much shorter than rise time, but i guess somebody thought at something else. However different resistor rating means the lower transistor needs much bigger peak rating, which is probably not true - more likely it has same peak rating as the upper one.

The transistors peak rating gives the values of resistors, e.g. the resistors are there to limit the peak current to a value just under the transistor's peak rating.

The R57 i guess its there to take out the parasitic uC outputs like some pins read 1-2v even when they are off or not in use, and that could be enough to enable the transistors.

If it is ensured by design that the transistors cant be both on at same time, then it should be safe to merge the 2 resistors into just one. If mosfets are used instead of transistors, then could get rid of the R53.

There are some pnp and npn paired together in an 6pin-8pin packages, for both transistors and fets, dunno if there are any matches for this specific (?3.3v), but probably worth taking a look - besides pairing characteristics its also convenient packaging - as long as the board can use the layout as it is, without any vias.

But, there should be no need to have the fall time with 2 paralel resistors, i dont see why. Normally the fall time is much shorter than rise time, but i guess somebody thought at something else. However different resistor rating means the lower transistor needs much bigger peak rating, which is probably not true - more likely it has same peak rating as the upper one.

The transistors peak rating gives the values of resistors, e.g. the resistors are there to limit the peak current to a value just under the transistor's peak rating.

The R57 i guess its there to take out the parasitic uC outputs like some pins read 1-2v even when they are off or not in use, and that could be enough to enable the transistors.

If it is ensured by design that the transistors cant be both on at same time, then it should be safe to merge the 2 resistors into just one. If mosfets are used instead of transistors, then could get rid of the R53.

There are some pnp and npn paired together in an 6pin-8pin packages, for both transistors and fets, dunno if there are any matches for this specific (?3.3v), but probably worth taking a look - besides pairing characteristics its also convenient packaging - as long as the board can use the layout as it is, without any vias.

Sorry, only registered users may post in this forum.